# Architecting the Future of AloT: Design and Implementation of RISC-V Edge Computers

Marcelo Zuffo mkzuffo@usp.br Universidade de São Paulo "People who are really serious about software should make their own hardware"

Alan Kay MIT

### Universidade de São Paulo

Interdisciplinary Center on Interactive Technologies CITI-USP

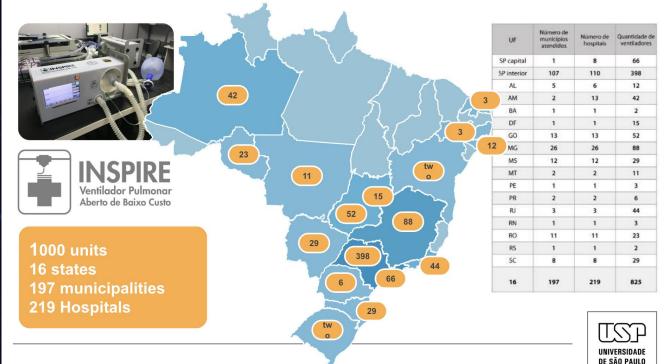

#### **EXAMPLES OF NATIONAL IMPACT**

NATIONAL COVERAGE USP PROJECTS

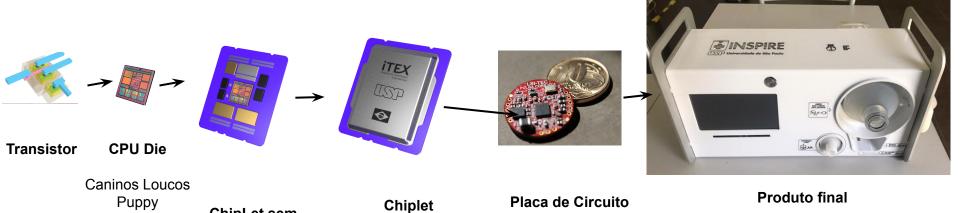

#### **INSPIRE Lung Ventilator:**

From conception to 3M certification in 100 days!

1,000 units manufactured and distributed in 16 states in Brazil

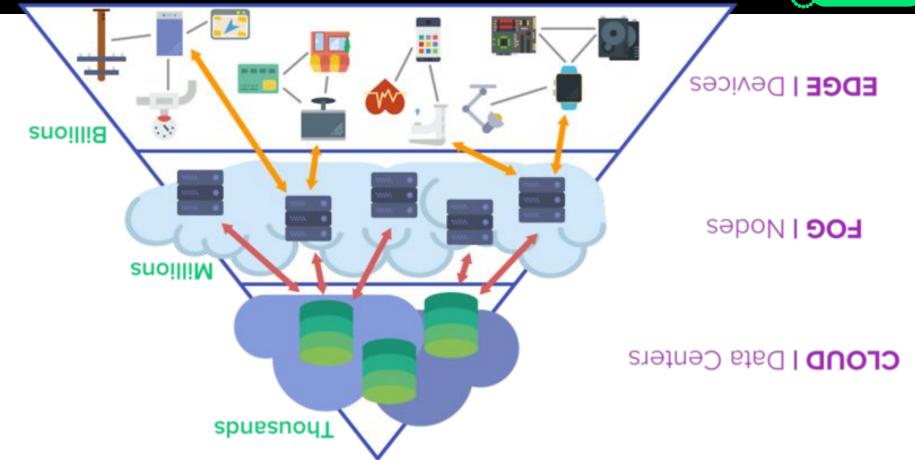

# Contexto

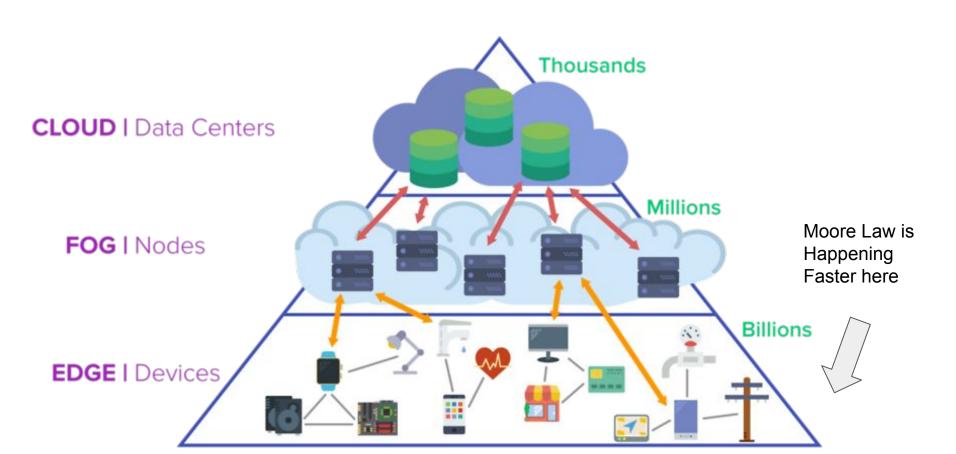

#### The CLOUD

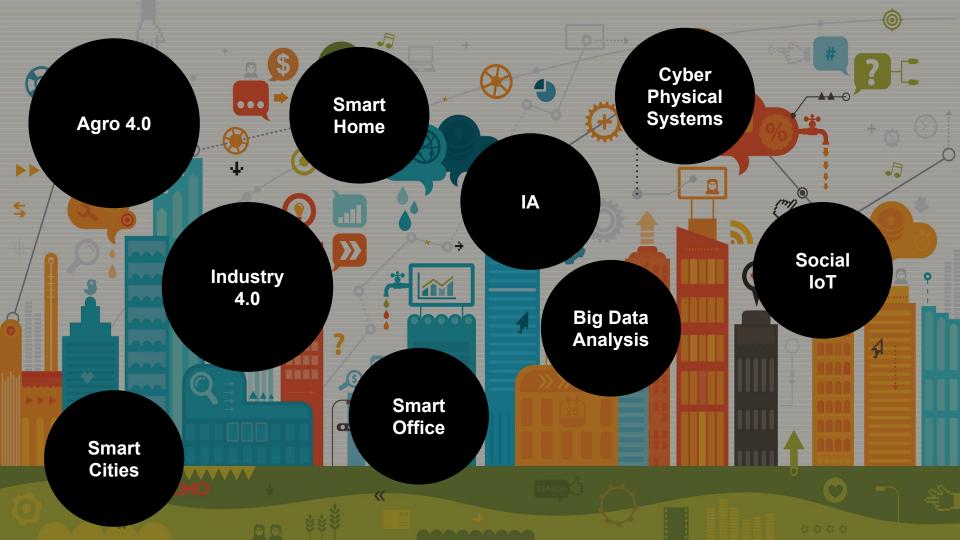

# The Cognitive Edge

# **Enabling Technologies**

Caninos Loucos www.caninosloucos.org

# Caninos Loucos Program Family

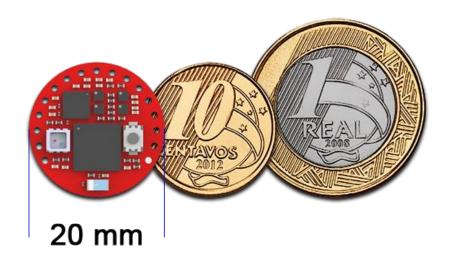

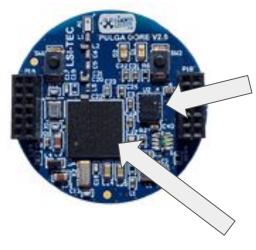

### **PULGA**

- porte pequeno

- tamanho de uma moeda

- autônoma

- baixo consumo

- captação de energia

- comunicação sem fio

- suporte a criptografia

### LABRADOR

- porte médio

- tamanho de um cartão de crédito

- processamento equivalente a um PC

- computação de propósito geral

- processamento de áudio e vídeo

- comunicação de banda larga

### **BANKHAR**

- porte grande

- sem restrição de tamanho

- computação de alto desempenho

- co-processamento programável

- múltiplos canais de comunicação

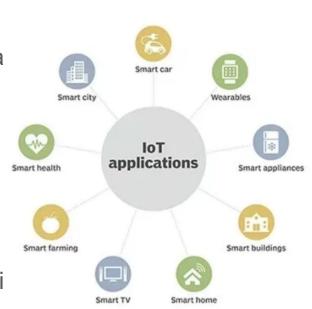

#### Contexto: IoT e semicondutores

#### Grandes oportunidades

IoT movimentará mais de US\$30Bi na América Latina até 2023

#### Smart Objects: bilhões de dispositivos

- eletrônica embarcada

- sensores / atuadores

- conectividade

Déficit da balança comercial eletro-eletrônica: US\$44Bi

- Tendência de maior demanda eletrônica

- Necessário estimular a produção nacional

# www.caninosloucos.org

- SBCs projetadas e manufaturadas no Brasil

- Hardware e Software abertos

- Foco na computação de borda

#### Objetivos do programa

Desenvolvimento e difusão de uma Plataforma Nacional de SBCs, através do projeto de componentes avançados de microeletrônica, consolidados em uma família de SBCs (Single Board Computers) de projeto nacional – desde o SoC, até a pilha de software, passando pela placa de circuito impresso e processos produtivos – para aplicações em Internet das Coisas.

### Fluxo do Produto de Hardware

ChipLet sem

encapsulamento

Ventilador Inspire

encapsulado

Impresso Montada

Caninos Loucos Pulga

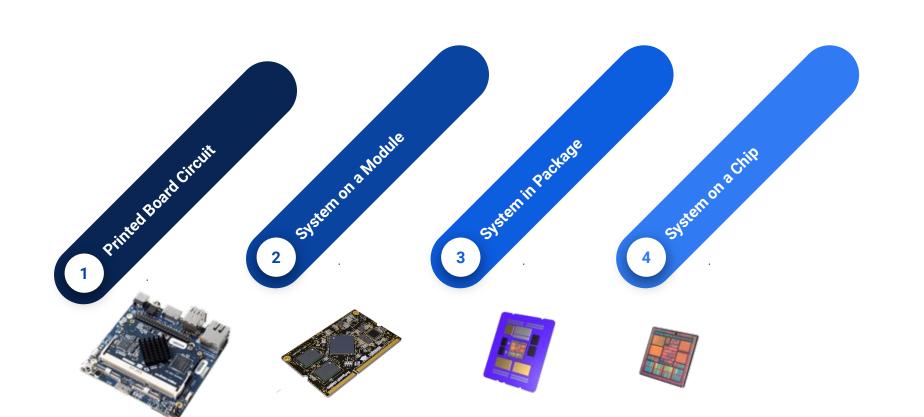

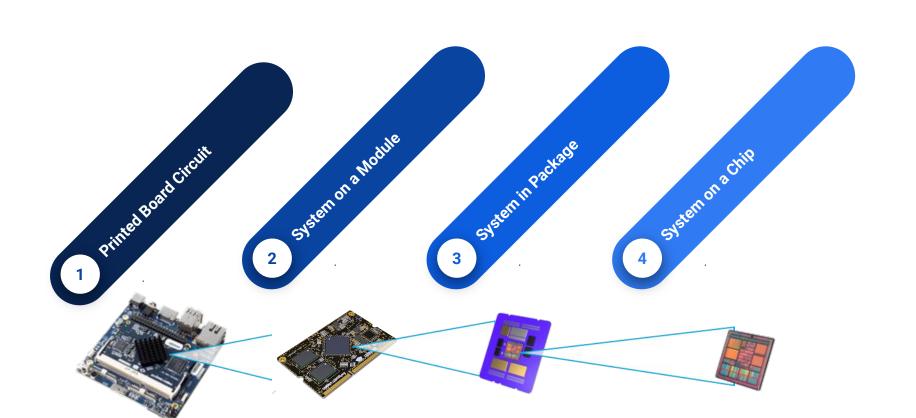

## Grau de integração de circuitos eletrônicos

## Grau de integração de circuitos eletrônicos

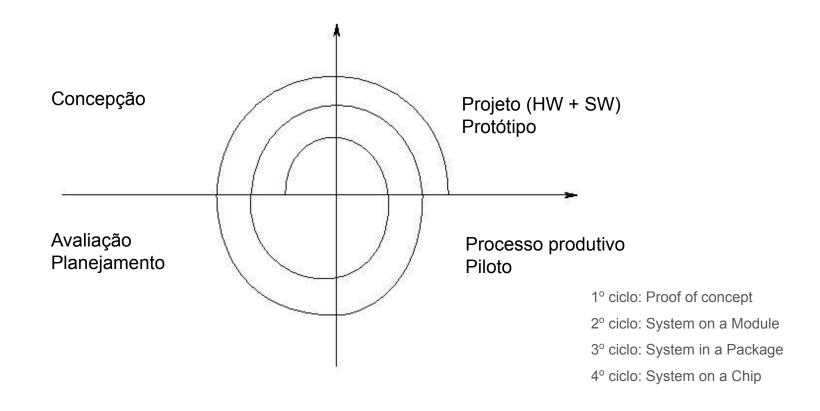

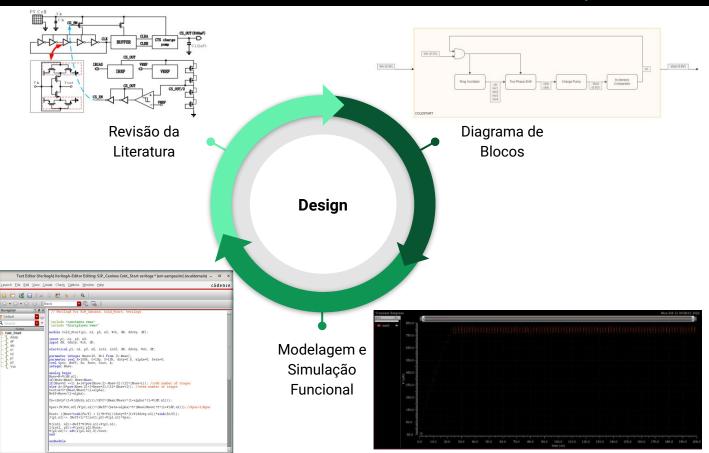

# Estratégia: desenvolvimento espiral

### A Família de SBCs

### **TINY**

- porte pequeno

- tamanho de uma moeda

- autônoma

- baixo consumo

- captação de energia

- comunicação sem fio

- suporte a criptografia

### MID

- porte médio

- tamanho de um cartão de crédito

- processamento equivalente a um PC

- computação de propósito geral

- processamento de áudio e vídeo

- comunicação de banda larga

### HIGH

- porte grande

- sem restrição de tamanho

- computação de alto desempenho

- co-processamento programável

- múltiplos canais de comunicação

SBC na Categoria Tiny

# Plataforma Tiny: conceito

- Tamanho reduzido

- Autonomia

- baixo consumo

- o captação de energia

- Comunicação sem fio

- Segurança e encriptação em hardware

- Utilização em prototipagem rápida (extensores)

# Plataformas SBC-Tiny

Pulga Core

Pulga Módulo

Pulga SiP

em desenvolvimento

## Extensibilidade da Pulga Core

- Placas de expansão

- LoRA WAN e harvesting solar

- 15 pinos de expansão (GPIO+energia)

- Storage Flash: 16MB

- Peso: 4g

- Dimensões: 20mm

#### Posicionamento GPS

- 15 pinos de expansão (GPIO+energia)

- Storage Flash: 16MB

- Peso: 4g

- Dimensões: 20mm

#### Sistemas Operacionais e Ambientes de Programação

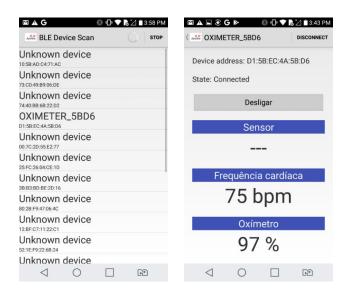

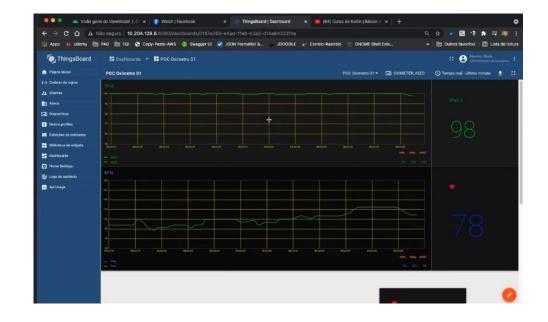

# Exemplos de aplicação: Sensores de Apnéia

Invólucros – Sensor de Respiração / Fivela Cinta Indutiva

### Sensores de Apneia

App Smartphone (Gateway)

Nuvem (Monitoramento Multiparamétrico)

# Pulga no rastreamento de tratores agrícolas

Rastreamento de tratores por Pulgas com GPS e LoRaWAN em fazendas produtoras de uvas Petrolina/PE

# Internet of Trees CO, Sensor

#### Monitoramento de florestas urbanas

- Sensores IoT manufaturados e em teste

- o CO,

- Umidade

- o Temperatura

- Incidência UV

LongRange ~40Km

ShortRange ~200M Bluetooh 4.0

Sensores

Co<sub>2</sub> (PPM)

H2O (%) Temp ©

Pressao

UV (lx)

Luz (lx)

Bateria LiPo ~1 Ano

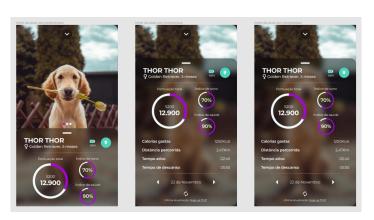

## Pulga para monitoramento animal

Produto de monitoramento de pets para bem estar animal

Empresa: Belka

# Caninos Loucos Pulga CI Design

# Caninos Loucos Pulga - IC Design

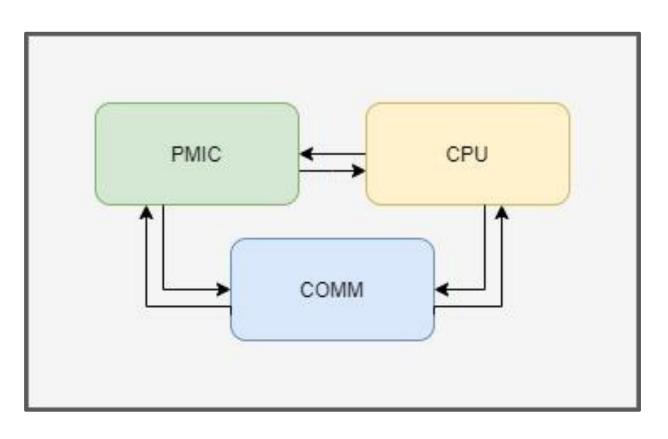

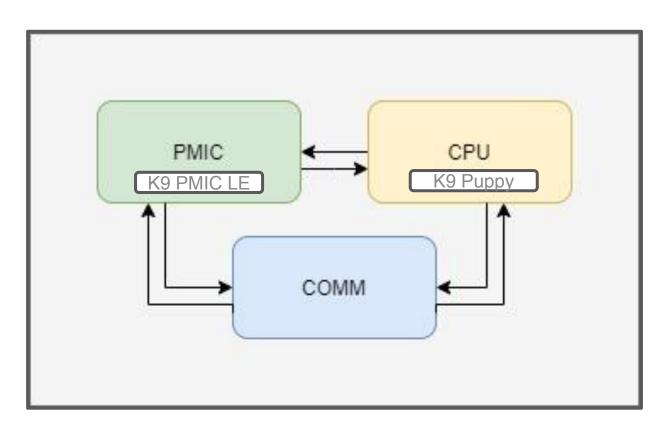

#### Caninos Loucos Pulga

PMIC Gerenciamento de energia

SoC:

CPU + Periféricos + Comunicação

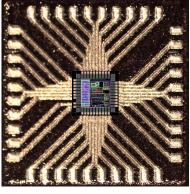

# System in package and chiplets

#### Chip composto

- encapsulamento com múltiplos dies internamente

- utiliza as tecnologias mais adequadas para cada módulo do sistema

# SBC-Tiny System in Package SiP

# SBC-Tiny System in Package SiP

#### SBC-Tiny System in Package SiP

# Design do Chip de Processamento

K9 Puppy para o Caninos Loucos Pulga

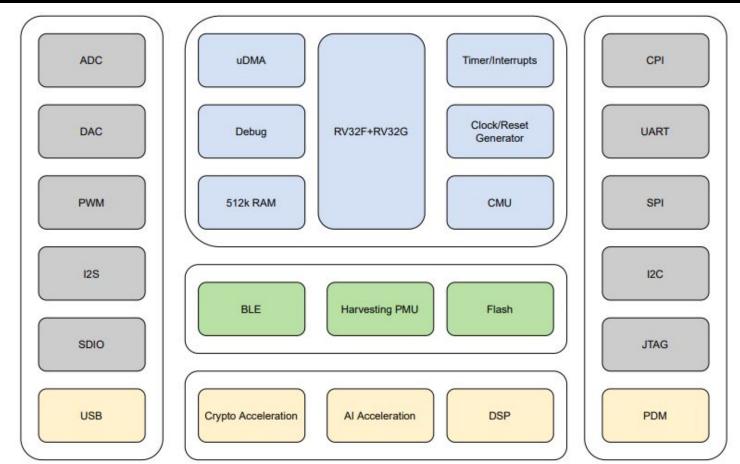

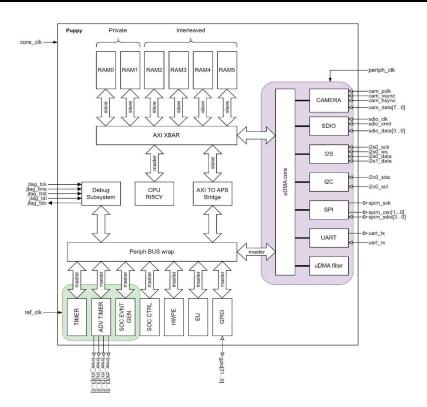

#### K9 Puppy RISC-V

- Criação de processador próprio e nacional.

- Foco em aplicações de borda.

- Utilização de núcleo RISC-V.

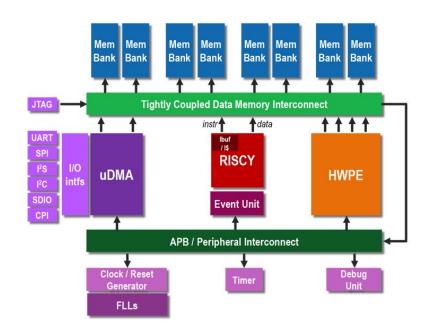

#### K9 Puppy RISC-V

- Escolha de arquitetura aberta para microprocessadores (RISC-V)

- Core RISCY 32 bits

- Presença de uDMA

- Acesso de periférico à memória sem intervenção do Core RISCY

- Conjunto de instruções livres e extensíveis.

- Flexibilidade para customização do processador.

- Periféricos modulares

- Potencialização de inovação

- Extensões bem definidas

- Acesso gratuito para desenvolvedores

- Disponibilidade de aplicações abertas e prontas para uso

- Aceleração no tempo de desenvolvimento

- Menor consumo de energia

- Padrão em crescimento no desenvolvimento de processadores

#### K9 Puppy RISC-V

- Microprocessador com tecnologia nacional

- Foco em aplicações de borda.

- Utilização de núcleo RISC-V.

Figure 1: Puppy's architecture

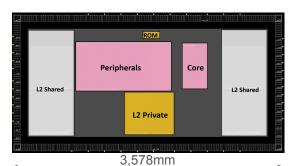

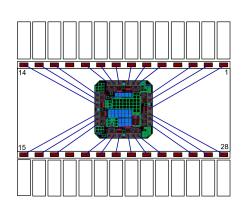

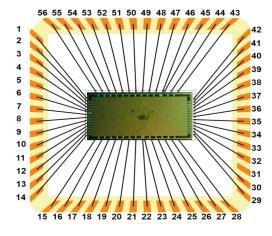

#### K9 Puppy V1.0

| PUPPY V1.0     |                                                                                                                                  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Technology     | UMC 65                                                                                                                           |  |

| Area           | 3597,6 um x1857,6 um                                                                                                             |  |

| Pins           | 56                                                                                                                               |  |

| Buttons        | (1) Reset                                                                                                                        |  |

| Encapsulation  | QFN                                                                                                                              |  |

| Lid            | Glue                                                                                                                             |  |

| Metal Layers   | 6                                                                                                                                |  |

| Clock          | Min:L 1MHZ<br>Typ: 20MHz<br>Max: 32MHZ                                                                                           |  |

| Other Features | uDMA for external memory<br>Camera interface<br>Cluster Bus Interface with 256KB of<br>Shared Memory<br>HW Accelerator Interface |  |

1,859mm

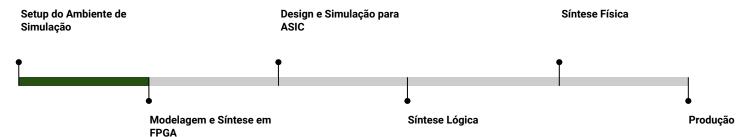

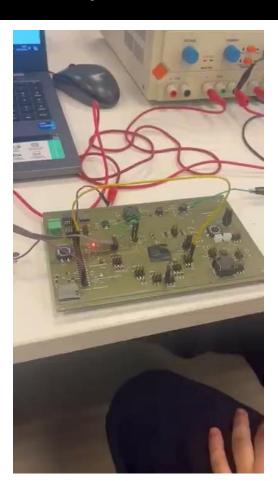

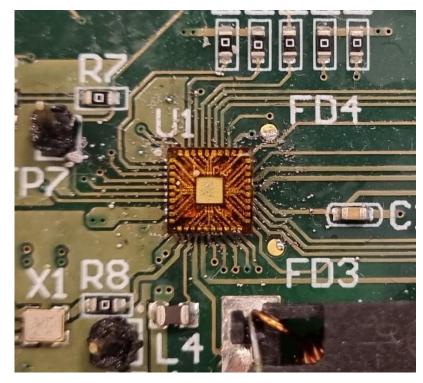

#### K9 Puppy Design

Modelagem e síntese em FPGA

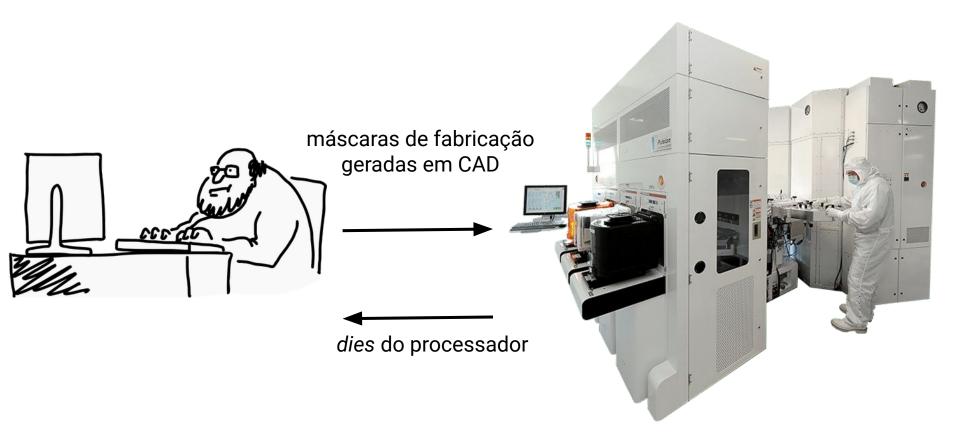

#### Fabricação dos CIs

#### Puppy funcional

coremark.txt 2K performance run parameters for coremark. CoreMark Size : 666 : 640720191 Total ticks Total time (secs): 32 : 62 Iterations/Sec : 2000 Iterations Compiler version: na Compiler flags : na Memory location : STATIC seedcrc : 0xe9f5 [0]crclist : 0xe714 [0]crcmatrix : 0x1fd7 : 0x8e3a [0] crcstate [0]crcfinal : 0x4983 Correct operation validated. See readme.txt for run and reporting rules. CoreMark 1.0 : 62 / na na / STATIC

Cores: 1 Threads: 1

Coremark score: 62 Coremark/MHz: 3.1

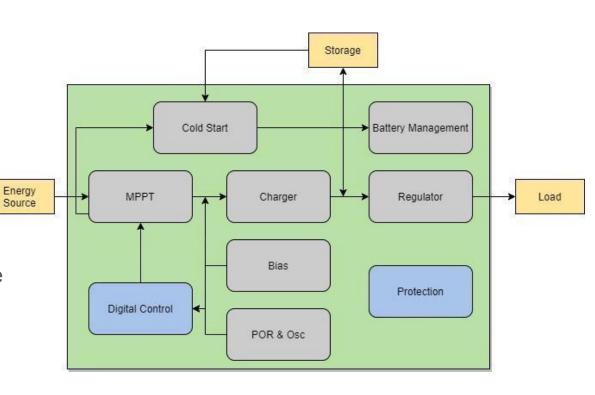

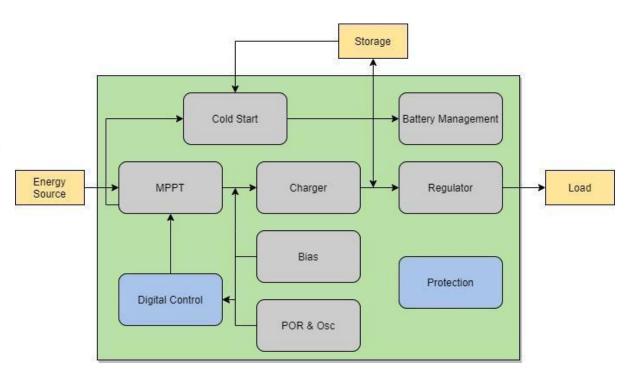

### Design do Chip de Gerenciamento de Energia

K9 PMIC LE para o Caninos Loucos Pulga

#### K9 PMIC LE

- Nível de Bateria via ADC

- I2C com o processador

- Reset de alta precisão

- Tensão de saída programável

- Harvesting e/ou bateria

- Tensão de referência e corrente de alimentação reguladas

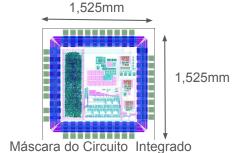

#### K9 PMIC LE V1.0

| PMIC v1           |                                                           |   |

|-------------------|-----------------------------------------------------------|---|

| Tensao de entrada | Analog: 1.8V<br>Dig: 1.8V/3.3V                            |   |

| Tensao de saida   | 1.8V                                                      |   |

| Dimensoes         | (6x6) mm                                                  |   |

| Peso              | -                                                         |   |

| Comm              | I2C, ADC 8 bits                                           |   |

| LED               |                                                           | 0 |

| Botoes            |                                                           | 0 |

| Sensores          | -                                                         |   |

| Consumo           | @48 MHz:<br>10.2 mW (máx com ADC em uso)                  |   |

|                   | 1.8V (analógico)<br>1.8V (digital)<br>3.3V (digital Pads) |   |

| GPIOs             |                                                           | 0 |

| clock             | Digital: 48 MHz<br>Analog: 1MHz                           |   |

| other features    | POR de alta precisão                                      |   |

#### K9 PMIC LE

Concepção e Modelagem

Esquemático e Simulação

Layout dos blocos

Integração Analógico-Digital

Produção

#### Resultados K9 PMIC LE

Layout do Circuito Integrado

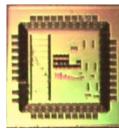

Pastilha Fotografada no Microscópio

### Design de SiP

Caninos Loucos Pulga

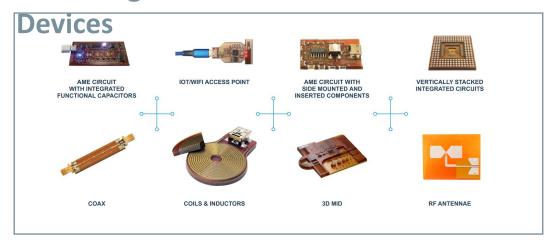

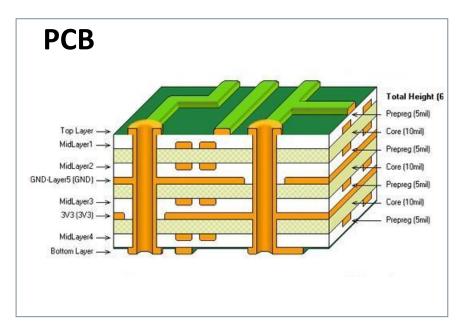

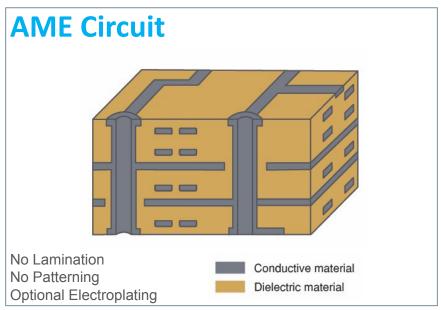

#### Manufatura Eletrônica Aditiva: Impressão microeletrônica 3D

#### **HiPED High Performance Electronic**

#### **Multilayer PCB**

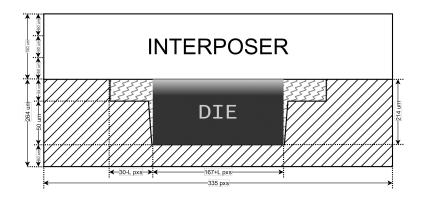

#### SiP Pulga em desenvolvimento

- >> Processo de embutir o chip na micro PCB

- >> Encapsulamento com a própria resina da PCB

## SiP por encapsulamento AME (Manufatura Eletrônica Aditiva)

#### Impressão 3D microeletrônica

Conventional designs are possible for AME. But think beyond limitations "freeform VIA"

### Thank you!